SSI Asynchronous Counters 3.2.2-3

|

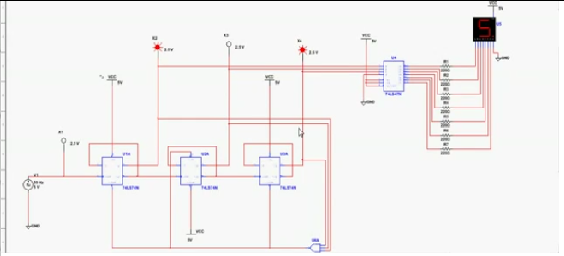

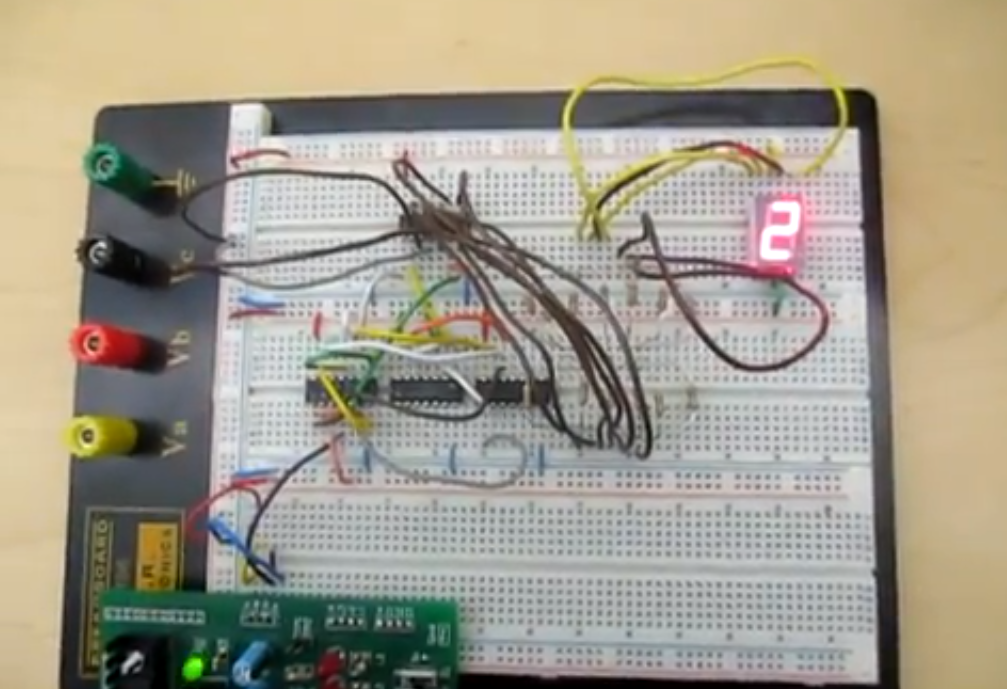

In this project we had to create a 3-bit-mod 6 up counter in Multisim, then we had to change it so that the circuit would start and end on different numbers. Once we were done making sure our circuit worked on Multisim we had to create the entire circuit on a breadboard, to ensure that it really did work. Then we had to recreate the circuit on Multisim so it could be downloaded to an FPGA board's programmable chip.

The design process for this circuit was fairly simple, three D-Flip Flops that halved the clock speed for every successive Flip-Flop, the three signals from the Flip-Flops then get sent to the part of the circuit that converts the signals to binary, which then go to the seven- segment L.E.D. display, in previous projects we had to kind of "invent" our own form of binary in order for the seven segment display to be able to read our signals but in this project we used a chip that converts the signals to binary by itself. To change what the counter ended on we had to put different types of logic gates such and ANDs, ORs, and INVERTERs so that when the signals got to the right combination of Highs and Lows it reset the entire circuit from zero. If I had to do this project again I would have made the breadboard a little more neat so that when my circuit failed (twice) I might have found the bug a little bit easier. |

|